1 月 31 日消息,英特爾代工服務(Intel Foundry)本周發布技術文檔,展示“AI 芯片測試載具”,用于驗證其在先進封裝領域的制造能力。

援引博文介紹,測試載具(Test Vehicle)并非是指最終上市銷售的商品,而是為了驗證制造工藝、設計思路是否可行而制造出來的“工程樣機”,就像汽車廠商發布的概念車或測試車。

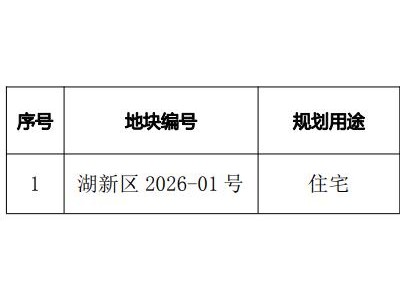

根據技術文檔,該測試載具的系統級封裝(SiP)擁有 8 倍光罩尺寸,內部集成了 4 個大型邏輯計算單元(Logic Tiles)、12 個 HBM4 級別的內存堆棧以及 2 個 I/O 單元。

值得注意的是,與上月展示的“16 邏輯單元 +24 內存堆棧”的概念模型不同,本次展示的方案代表了英特爾目前已實際具備的量產制造能力。

在核心工藝上,該測試平臺的核心邏輯單元采用了英特爾最先進的 18A 工藝,集成了 RibbonFET 全環繞柵極晶體管和 PowerVia 背面供電技術。

在芯片互連方面,英特爾采用了 EMIB-T 2.5D 嵌入式橋接技術。通過在橋接器內部添加硅通孔(TSV),電力和信號不僅可以橫向傳輸,還能實現垂直傳輸,從而最大化互連密度,設計支持高達 32 GT/s 的 UCIe 接口標準。

芯片堆疊方面,英特爾將利用 Foveros 3D 封裝技術(包括 Foveros 2.5D、Foveros-R 和 Foveros Direct 3D)實現垂直堆疊芯粒(Chiplets),底層的 18A-PT 基礎芯片(Base Dies)位于計算芯片下方,可充當大容量緩存或處理額外任務。

供電方面,英特爾將支持支持“Semi”集成電壓調節器(IVR),并利用嵌入式同軸磁性電感器(CoaxMIL)和多層電容網絡(如 Omni MIM),集成全套供電創新技術。

與臺積電 CoWoS-L 將電壓調節器置于中介層不同,英特爾將其置于每個堆棧及封裝下方。這種設計旨在應對生成式 AI 負載產生的瞬時電流波動,確保在不損失電壓余量的情況下提供清潔、穩定的電力。